# **Introduction to Parallel Processing**

# Norman Matloff Department of Computer Science University of California at Davis ©1995-2006, N. Matloff

# March 28, 2006

# **Contents**

| 1 | Ove                   | rview   |                                            | 3  |  |  |  |

|---|-----------------------|---------|--------------------------------------------|----|--|--|--|

| 2 | Programming Paradigms |         |                                            |    |  |  |  |

|   | 2.1                   | World   | Views                                      | 4  |  |  |  |

|   |                       | 2.1.1   | Shared-Memory                              | 4  |  |  |  |

|   |                       | 2.1.2   | Message Passing                            | 5  |  |  |  |

|   |                       | 2.1.3   | SIMD                                       | 5  |  |  |  |

|   | 2.2                   | Shared  | l-Memory Example                           | 6  |  |  |  |

|   |                       | 2.2.1   | How Threads Work on Multiprocessor Systems | 6  |  |  |  |

|   |                       | 2.2.2   | Example                                    | 7  |  |  |  |

|   | 2.3                   | Messa   | ge-Passing Example                         | 10 |  |  |  |

| 3 | Mes                   | sage-Pa | ssing Mechanisms                           | 14 |  |  |  |

|   | 3.1                   | Messa   | ge-Passing Hardware                        | 14 |  |  |  |

|   |                       | 3.1.1   | Hypercubes                                 | 14 |  |  |  |

|   |                       | 3.1.2   | Networks of Workstations (NOWs)            | 16 |  |  |  |

|   |                       | 3.1.3   | Hardware Issues                            | 17 |  |  |  |

|   |                       | 3.1.4   | Message Passing on Shared-Memory Machines  | 18 |  |  |  |

CONTENTS

|   | 3.2  | Message-Passing Software |                                               |    |  |  |  |

|---|------|--------------------------|-----------------------------------------------|----|--|--|--|

| 4 | Shai | Shared-Memory Mechanisms |                                               |    |  |  |  |

|   | 4.1  | Hardw                    | are Issues                                    | 18 |  |  |  |

|   | 4.2  | Shared                   | l-Memory through Hardware                     | 18 |  |  |  |

|   |      | 4.2.1                    | Placement of Memory Modules                   | 19 |  |  |  |

|   |      | 4.2.2                    | Interconnect Topologies                       | 21 |  |  |  |

|   |      | 4.2.3                    | Test-and-Set                                  | 25 |  |  |  |

|   |      | 4.2.4                    | Cache Coherency                               | 26 |  |  |  |

|   |      | 4.2.5                    | The Problem of "False Sharing"                | 30 |  |  |  |

|   |      | 4.2.6                    | Memory-Access Consistency Policies            | 30 |  |  |  |

|   |      | 4.2.7                    | Fetch-and-Add and Packet-Combining Operations | 32 |  |  |  |

|   |      | 4.2.8                    | Multicore Chips                               | 33 |  |  |  |

|   |      | 4.2.9                    | Software for Use with Shared-Memory Hardware  | 33 |  |  |  |

|   | 4.3  | Shared                   | l-Memory through Software                     | 37 |  |  |  |

|   |      | 4.3.1                    | Software Distributed Shared Memory            | 37 |  |  |  |

|   |      | 4.3.2                    | Case Study: JIAJIA                            | 39 |  |  |  |

| 5 | Prog | gram Pe                  | erformance Issues                             | 42 |  |  |  |

|   | 5.1  | The Pr                   | oblem                                         | 42 |  |  |  |

|   | 5.2  | Some '                   | Timing Comparisons                            | 43 |  |  |  |

|   | 5.3  | Solution                 | ons                                           | 44 |  |  |  |

|   | 5.4  | Time N                   | Measurement                                   | 44 |  |  |  |

| 6 | Deb  | ugging ?                 | Multicomputer Programs                        | 44 |  |  |  |

| 7 | Barı | rier Im <sub>l</sub>     | plementation                                  | 46 |  |  |  |

|   | 7.1  | A Use                    | -Once Version                                 | 46 |  |  |  |

|   | 7.2  | An Att                   | tempt to Write a Reusable Version             | 46 |  |  |  |

#### 1 Overview

There is an ever-increasing appetite among computer users for faster and faster machines. This was epitomized in a statement by Steve Jobs, founder/CEO of Apple and Pixar. He noted that when he was at Apple in the 1980s, he was always worried that some other company would come out with a faster machine than his. But now at Pixar, whose graphics work requires extremely fast computers, he is always <u>hoping</u> someone produces faster machines, so that he can use them!

A major source of speedup is the parallelizing of operations. Parallel operations can be either within-processor, such as with pipelining or having several ALUs within a processor, or between-processor, in which many processor work on different parts of a problem in parallel. Our focus here is on between-processor operations.

For example, the Registrar's Office at UC Davis uses shared-memory multiprocessors for processing its on-line registration work. A shared-memory multiprocessor machine consists of several processors, plus a lot of memory, all connected to the same bus or other interconnect. All processors then access the same memory chips. As of March 2004, the Registrar's current system was a SPARC Sunfire 3800, with 16 GB RAM and eight 900 MHz UltraSPARC III+ CPUs.<sup>1</sup>

Online registration involves an enormous amount of database computation. In order to handle this computation reasonably quickly, the program partitions the work to be done, assigning different portions of the database to different processors. Currently database work comprises the biggest use of shared-memory parallel machines. It is due to the database field that such machines are now so successful commercially.

As the Pixar example shows, highly computation-intensive applications like computer graphics also have a need for these fast parallel computers. No one wants to wait hours just to generate a single image, and the use of parallel processing machines can speed things up considerably. For example, consider **ray tracing** operations. Here our code follows the path of a ray of light in a scene, accounting for reflection and absorbtion of the light by various objects. Suppose the image is to consist of 1,000 rows of pixels, with 1,000 pixels per row. In order to attack this problem in a parallel processing manner with, say, 25 processors, we could divide the image into 25 squares of size 200x200, and have each processor do the computations for its square.<sup>2</sup>

Parallel processing machines tend to be quite expensive, but another popular platform for parallel processing which is much cheaper is a network of workstations (NOW). Here the hardware consists of a set of computers which happen to be connected via a network, such as in our Computer Science Instructional Facility (CSIF) at UCD.<sup>3</sup> Most of the time these machines are used independently, with the role of the network being for e-

<sup>&</sup>lt;sup>1</sup>You might consider 900 MHz somewhat slow, ironic for a machine whose goal is speed. But speeds for RISC chips such as the SPARC cannot be easily compared with those of CISC chips like Intel. Moreover, these systems have especially fast I/O, which is crucial for database applications. That, together with the fact that we have many processors working in parallel, does indeed make for a very fast machine.

It is true, though, that Sun probably has faster SPARCs than 900 MHz. The problem is that in a multiprocessor system, the processors must really be tuned to each other, and thus one cannot easily substitute newer, faster processors when they are developed.

<sup>&</sup>lt;sup>2</sup>As we'll see later, it may be much more challenging than this implies. First of all, the computation will need some communication between the processors, which harms performance if it is not done carefully. Second, if one really wants a good speedup, one may need to take into account the fact that some squares require more computation work than others. More on this below.

<sup>&</sup>lt;sup>3</sup>If one really wants a good NOW, though, one would need to have a faster network than CSIF's.

mail, file sharing, Internet connections and so on. But they are sometimes also used for parallel processing, with the network being used to pass messages between various machines which are cooperating on the same task; a NOW is thus an example of **message-passing hardware**.

Remember, the reason for buying a parallel processing machine is *speed*. You need to have a program that runs as fast as possible. That means that in order to write good parallel processing software, you must have a good knowledge of the underlying hardware. You must find also think of clever tricks for **load balancing**, i.e. keeping all the processors busy as much as possible. In the graphics ray-tracing application, for instance, suppose a ray is coming from the "northeast" section of the image, and is reflected by a solid object. Then the ray won't reach some of the "southwest" portions of the image, which then means that the processors assigned to those portions will not have any work to do which is associated with this ray. What we need to do is then try to give these processors some other work to do; the more they are idle, the slower our system will be.

# 2 Programming Paradigms

There are two main paradigms today in parallel-processing, **shared memory** and **message passing**. These distinctions can occur at either the software or hardware level. In other words, both software and hardware can be designed around both the shared-memory and message-passing paradigms. Thus for example, the UCD Registrar could run message-passing software such as the MPI package on their shared-memory hardware, while we could use the shared-memory software package Treadmarks on the message-passing NOW in CSIF.

#### 2.1 World Views

To explain the two paradigms, we will use the term **nodes**, where roughly speaking one node corresponds to one processor, and use the following example:

Suppose we wish to multiply an nx1 vector X by an nxn matrix A, putting the product in an nx1 vector Y, and we have p processors to share the work.

#### 2.1.1 Shared-Memory

In the shared-memory paradigm, the arrays for A, X and Y would be held in common by all nodes. If for instance node 2 were to execute

```

Y[3] = 12;

```

and then node 15 were to subsequently execute

```

print("%d\n",Y[3]);

```

then the outputted value from the latter would be 12.

#### 2.1.2 Message Passing

By contrast, in the message-passing paradigm, all nodes would have <u>separate</u> copies of A, X and Y (or maybe some nodes would not even have some or all of these arrays). In this case, in our example above, in order for node 2 to send this new value of Y[3] to node 15, it would have to execute some special function, which would be something like

```

send(15,12,"Y[3]");

```

and node 15 would have to execute some kind of receive() function.

The conventional wisdom is that the shared-memory paradigm is much easier to program in than the message-passing paradigm. The latter, however, may be easier to implement, and in some settings may have greater speed.

#### 2.1.3 SIMD

Another paradigm is **Single Instruction, Multiple Data** (SIMD). This is almost entirely a hardware issue. You can think of it as a processor with a very large number of ALUs, except that they do not operate independently. Whenever the CPU issues an instruction, that same instruction is executed in lockstep by all the ALUs. Another difference is that each ALU has its own data registers.

In classical SIMD machines, the ALUs are arranged in a two-dimensional array. A typical instruction might be, say, SENDLEFT, which would mean sending the value in the ALU's register to the ALU on one's left (or nowhere, if the ALU is on the left edge).

This is common in image-processing applications, for example. Say we have one ALU per pixel and we wish to replace each pixel value by the average of its neighboring values. The code might look like this:

```

set sum to 0 add left neighbor to sum add right neighbor to sum add top neighbor to sum add bottom neighbor to sum divide sum by 4

```

Again, remember that this is occurring simultaneously at all the ALUs, i.e. at all the pixels.

Some of the "MMX"-style chips operate under the SIMD paradigm.

#### 2.2 Shared-Memory Example

Today, programming on shared-memory multiprocessors is typically done via **threading**. A **thread** is similar to a **process** in an operating system (OS), but with much less overhead. Threaded applications have become quite popular in even uniprocessor systems, and Unix, Windows, Python, Java and Perl all support threaded programming. One of the most famous threads packages is Pthreads.

#### 2.2.1 How Threads Work on Multiprocessor Systems

Even if you have had some exposure to threaded programming before, it's important to understand how things change when we use it in a multiprocessor environment. To this end, let's first review how an OS schedules processes on a uniprocessor system.

Say persons X and Y are both running programs on the same uniprocessor machine. Since there is only one CPU, only one program is running at any given time, but they do "take turns." X's program will run for a certain amount of time, which we'll assume for concreteness is 50 milliseconds. After 50 milliseconds, a hardware timer will issue an interrupt, which will cause X's program to suspend and the OS to resume execution. The **state** of X's program at the time of the interrupt, i.e. the values in the registers etc., will be saved by the OS, and the OS will then restore the state of Y's program which had been saved at its last turn. Finally, the OS will execute a interrupt-return instruction, which will cause Y's program to restore execution in exactly the setting which it had at the end of its last turn. Note also that if the program which is currently running makes a **system call**, i.e. calls a function in the OS for input/output or other services, the program's turn ends before 50 ms.

But again, at any given time only one of the three programs (X, Y and the OS) is running. By contrast, on a multiprocessor system with k CPUs, at any given time k programs are running. When a turn for a program ends on a given CPU, again an interrupt occurs and the OS resumes execution, at which time it looks for another program to run.

Though we have been speaking in terms of programs, the proper term is **processes**. Say for instance that three people are running the GCC compiler right now on a certain machine. That would be only one program but three processes.

For the type of threads we are discussing here—**nonpreemptive** and system level—a thread essentially is a process. If for instance a program creates four threads, then all four will show up when one runs the **ps** command on a Unix system. The difference is that threads have much less overhead than do ordinary processes.

Threaded programming is natural for shared-memory multiprocessors, since it does share memory.<sup>4</sup> Just like the process pool is shared by all the processors, so is the thread pool. Whenever a processor finishes a timeslice for a thread, it goes to the thread pool to find another one to process. In that manner, there usually will be many threads executing truly simultaneously, i.e. we get real parallelism.

<sup>&</sup>lt;sup>4</sup>On Unix systems, one can arrange for shared memory between processes by using **shmem**(). However, it has poor peformance and is unwieldy. It is much easier, more direct and more natural with threads.

#### 2.2.2 Example

Here is an example of Pthreads programming:

```

// PrimesThreads.c

// threads-based program to find the number of primes between 2 and n;

// uses the Sieve of Eratosthenes, deleting all multiples of 2, all

// multiples of 3, all multiples of 5, etc.

// for illustration purposes only; NOT claimed to be efficient

8

// Unix compilation: gcc -g -o primesthreads PrimesThreads.c -lpthread -lm

9

10

11

// usage: primesthreads n

12

#include <stdio.h>

13

#include <math.h>

14

#include <pthread.h> // required for threads usage

15

#define MAX_N 100000000

17

#define MAX_THREADS 25

18

19

// shared variables

20

int nthreads, // number of threads (not counting main())

21

n, // range to check for primeness

22

23

prime[MAX_N+1], // in the end, prime[i] = 1 if i prime, else 0

24

nextbase; // next sieve multiplier to be used

// lock for the shared variable nextbase

pthread_mutex_t nextbaselock = PTHREAD_MUTEX_INITIALIZER;

26

// ID structs for the threads

27

pthread_t id[MAX_THREADS];

28

29

// "crosses out" all odd multiples of k

30

void crossout(int k)

31

{ int i;

32

for (i = 3; i*k <= n; i += 2)

33

prime[i*k] = 0;

34

35

}

36

37

// each thread runs this routine

void *worker(int tn) // tn is the thread number (0,1,...)

39

int lim, base,

40

work = 0; // amount of work done by this thread

41

\//\ no need to check multipliers bigger than sqrt(n)

42

lim = sqrt(n);

43

44

// get next sieve multiplier, avoiding duplication across threads

45

// lock the lock

46

47

pthread_mutex_lock(&nextbaselock);

base = nextbase;

48

nextbase += 2;

49

// unlock

50

```

```

pthread_mutex_unlock(&nextbaselock);

51

if (base <= lim)</pre>

52

work++; // log work done by this thread

53

// don't bother crossing out if base known composite

54

if (prime[base]) crossout(base);

55

56

57

else return work;

} while (1);

58

}

59

60

main(int argc, char **argv)

61

{ int nprimes, // number of primes found

62

63

i,work;

n = atoi(argv[1]);

64

nthreads = atoi(argv[2]);

65

// mark all even numbers nonprime, and the rest "prime until

66

// shown otherwise"

67

for (i = 3; i \le n; i++) {

68

if (i\%2 == 0) prime[i] = 0;

else prime[i] = 1;

70

}

71

nextbase = 3;

72

// get threads started

73

for (i = 0; i < nthreads; i++)</pre>

74

// this call says to create a thread, record its ID in the array

75

// id, and get the thread started executing the function worker(),

76

// passing the argument i to that function

77

pthread_create(&id[i],NULL,worker,i);

78

}

79

80

81

// barrier, to wait for all done

82

for (i = 0; i < nthreads; i++)

// this call said to wait until thread number id[i] finishes

83

// execution, and to assign the return value of that thread to our

84

// local variable work here

85

pthread_join(id[i],&work);

86

printf("%d values of base done\n",work);

87

}

89

// report results

90

nprimes = 1;

91

for (i = 3; i \le n; i++)

92

if (prime[i])

93

94

nprimes++;

95

printf("the number of primes found was %d\n",nprimes);

96

97

}

98

```

To make our discussion concrete, suppose we are running this program with two threads. Suppose also the both threads are simultaneously most of the time. This will occur if they aren't competing for turns with other big threads. That in turn will occur if there are no other big threads, or more generally if the number of other big threads is less than or equal to the number of processors minus two.

Note the global variables:

```

int nthreads, // number of threads (not counting main())

n, // range to check for primeness

prime[MAX_N+1], // in the end, prime[i] = 1 if i prime, else 0

nextbase; // next sieve multiplier to be used

pthread_mutex_t nextbaselock = PTHREAD_MUTEX_INITIALIZER;

pthread_t id[MAX_THREADS];

```

This will require some adjustment for those who've been taught that global variables are "evil." All communication between processors in shared-memory systems<sup>5</sup> is via global variables, so if they are evil, they are a necessary evil. Personally I think there is nothing wrong with global variables anyway. See http://heather.cs.ucdavis.edu/~matloff/globals.html.

As mentioned earlier, these are shared by all processors.<sup>6</sup> If one processor, for instance, assigns the value 0 to **prime[35]** in the function **crossout()**, then that variable will have the value 0 when accessed by any of the other processors as well. On the other hand, local variables have different values at each processor; for instance, the variable **i** in that function has a different value at each processor.

In the code

```

pthread_mutex_lock(&nextbaselock);

base = nextbase

nextbase += 2

pthread_mutex_unlock(&nextbaselock);

```

we see a **critical section** operation which is typical in shared-memory programming. In this context here, it means that we cannot allow more than one thread to execute

```

base = nextbase;

nextbase += 2;

```

at the same time. The calls to **pthread\_mutex\_lock()** and **pthread\_mutex\_unlock()** ensure this. If thread A is currently executing inside the critical section and thread B tries to lock the lock by calling **pthread\_mutex\_lock()**, the call will block until thread B executes **pthread\_mutex\_unlock()**.

Here is why this is so important: Say currently **nextbase** has the value 11. What we want to happen is that the next thread to read **nextbase** will then "cross out" all multiples of 11. But if we allow two threads to execute the critical section at the same time, the following may occur:

- thread A reads **nextbase**, setting its value of **base** to 11

- thread B reads **nextbase**, setting its value of **base** to 11

<sup>&</sup>lt;sup>5</sup>And for that matter, within threaded programs on uniprocessor systems.

<sup>&</sup>lt;sup>6</sup>Technically, we should say "shared by all threads" here, as a given thread does not always execute on the same processor, but at any instant in time each executing thread is at some processor, so the statement is all right.

- thread A adds 2 to **nextbase**, so that **nextbase** becomes 13

- thread B adds 2 to **nextbase**, so that **nextbase** becomes 15

Two problems would then occur:

- Both threads would do "crossing out" of multiples of 7, thus duplicating and thus a slowing down execution speed.

- We will never "cross out" multiples of 13.

Thus the lock is crucial to the correct (and speedy) execution of the program.

Note the barrier:

```

for (i = 0; i < nthreads; i++) {

pthread_join(id[i],&work);

printf("%d values of base done\n",work);

}</pre>

```

Ignore the **printf**() call; the main purpose of this loop is to wait for all threads to finish. This is needed in order to prevent premature execution of the later code

```

for (i = 3; i <= n; i++)

if (prime[i]) {

nprimes++;

}</pre>

```

resulting in possibly wrong output if we start counting primes before some threads are done.

Actually, barriers are more general than this. A barrier is simply a point in the code at which we must wait for all threads to reach before continuing. The threads do not necessarily have to exit at that point, as they do here. This is a very common operation in shared-memory programming, which we will return to later.

#### 2.3 Message-Passing Example

Here we use the MPI system, a popular public-domain set of interface functions, callable from C/C++, to do message passing. We are again counting primes, though in this case using a **pipelining** method. It is similar to hardware pipelines, but in this case it is done in software, and each "stage" in the pipe is a different computer.

The program is self-documenting, via the comments.

```

/* this include file is mandatory */

#include <mpi.h>

2

3

/* MPI sample program; NOT INTENDED TO BE EFFICIENT as a prime

4

finder, either in algorithm or implementation

5

6

7

MPI (Message Passing Interface) is a popular package using

the "message passing" paradigm for communicating between

8

processors in parallel applications; as the name implies,

9

processors communicate by passing messages using "send" and

10

"receive" functions

11

finds and reports the number of primes less than or equal to N

13

14

uses a pipeline approach: node 0 looks at all the odd numbers

15

(i.e. has already done filtering out of multiples of 2) and

16

filters out those that are multiples of 3, passing the rest

17

to node 1; node 1 filters out the multiples of 5, passing

18

19

the rest to node 2; in this simple example, we just have node

2 filter out all the rest and then report the number of primes

20

21

note that we should NOT have a node run through all numbers

22

before passing them on to the next node, since we would then

23

have no parallelism at all; on the other hand, passing on just

24

one number at a time isn't efficient either, due to the high

overhead of sending a message if it is a network (tens of

26

microseconds until the first bit reaches the wire, due to

27

software delay); thus efficiency would be greatly improved if

28

each node saved up a chunk of numbers before passing them to

29

the next node */

30

31

32

#define MAX_N 100000

#define PIPE_MSG 0 /* type of message containing a number to

33

be checked */

34

#define END_MSG 1 /* type of message indicating no more data will

35

be coming */

36

37

int NNodes, /* number of nodes in computation*/

38

N, /* find all primes from 2 to N */

39

/* my node number */

40

ToCheck; /* current number to check for passing on to next node;

41

stylistically this might be nicer as a local in

42

Node*(), but I have placed it here to dramatize

43

the fact that the globals are NOT shared among

44

45

the nodes */

double T1, T2; /* start and finish times */

47

48

Init(Argc,Argv)

49

int Argc; char **Argv;

50

51

int DebugWait;

52

53

N = atoi(Argv[1]);

54

DebugWait = atoi(Argv[2]);

55

```

```

56

/* this loop is here to synchronize all nodes for debugging;

57

if DebugWait is specified as 1 on the command line, all nodes

58

wait here until the debugging programmer starts GDB at all

59

nodes and within GDB sets DebugWait to 0 to then proceed */

60

while (DebugWait) ;

62

/* mandatory to begin any MPI program */

63

MPI_Init(&Argc,&Argv);

64

65

/* puts the number of nodes in NNodes */

66

MPI_Comm_size(MPI_COMM_WORLD,&NNodes);

/* puts the node number of this node in Me */

68

MPI_Comm_rank(MPI_COMM_WORLD,&Me);

69

70

/* OK, get started; first record current time in T1 */

71

if (Me == 2) T1 = MPI_Wtime();

72

73

}

74

Node0()

75

76

int I, Dummy,

77

Error; /* not checked in this example */

78

for (I = 1; I <= N/2; I++) {

79

ToCheck = 2 * I + 1;

80

if (ToCheck > N) break;

81

/* MPI_Send -- send a message

82

parameters:

83

pointer to place where message is to be drawn from

84

number of items in message

85

86

item type

87

destination node

message type ("tag") programmer-defined

88

node group number (in this case all nodes) */

89

if (ToCheck % 3 > 0)

90

Error = MPI_Send(&ToCheck,1,MPI_INT,1,PIPE_MSG,MPI_COMM_WORLD);

91

92

Error = MPI_Send(&Dummy,1,MPI_INT,1,END_MSG,MPI_COMM_WORLD);

93

}

94

95

Node1()

96

97

int Error, /* not checked in this example */

98

99

Dummy;

MPI_Status Status; /* see below */

100

101

while (1) {

102

/* MPI_Recv -- receive a message

103

parameters:

104

pointer to place to store message

105

number of items in message (see notes on

106

this at the end of this file)

107

item type

108

accept message from which node(s)

109

message type ("tag"), programmer-defined (in this

110

```

```

case any type)

111

node group number (in this case all nodes)

112

status (see notes on this at the end of this file) */

113

Error = MPI_Recv(&ToCheck,1,MPI_INT,0,MPI_ANY_TAG,

114

MPI_COMM_WORLD,&Status);

115

116

if (Status.MPI_TAG == END_MSG) break;

117

if (ToCheck % 5 > 0)

Error = MPI_Send(&ToCheck,1,MPI_INT,2,PIPE_MSG,MPI_COMM_WORLD);

118

119

/* now send our end-of-data signal, which is conveyed in the

120

message type, not the message (we have a dummy message just

121

as a placeholder */

122

Error = MPI_Send(&Dummy,1,MPI_INT,2,END_MSG,MPI_COMM_WORLD);

123

}

124

125

Node2()

126

127

int ToCheck, /* current number to check from Node 0 */

128

129

Error, /* not checked in this example */

PrimeCount,I,IsComposite;

130

MPI_Status Status; /* see below */

131

132

PrimeCount = 3; /* must account for the primes 2, 3 and 5, which

133

won't be detected below */

134

while (1)

135

Error = MPI_Recv(&ToCheck,1,MPI_INT,1,MPI_ANY_TAG,

136

MPI_COMM_WORLD,&Status);

137

if (Status.MPI_TAG == END_MSG) break;

138

IsComposite = 0;

139

for (I = 7; I*I \leftarrow ToCheck; I += 2)

140

141

if (ToCheck % I == 0) {

142

IsComposite = 1;

break;

143

}

144

if (!IsComposite) PrimeCount++;

145

146

/* check the time again, and subtract to find run time */

147

T2 = MPI_Wtime();

148

printf("elapsed time = %f\n",(float)(T2-T1));

149

/* print results */

150

printf("number of primes = %d\n",PrimeCount);

151

}

152

153

154

main(argc,argv)

155

int argc; char **argv;

156

Init(argc,argv);

157

/* note: instead of having a switch statement, we could write

158

three different programs, each running on a different node */

159

switch (Me)

160

case 0: Node0();

161

break;

162

case 1: Node1();

163

break;

164

case 2: Node2();

165

```

```

166

/* mandatory for all MPI programs */

167

MPI_Finalize();

168

}

169

170

171

/* explanation of "number of items" and "status" arguments at the end

172

of MPI_Recv():

173

when receiving a message you must anticipate the longest possible

174

message, but the actual received message may be much shorter than

175

this; you can call the MPI_Get_count() function on the status

176

argument to find out how many items were actually received

177

178

the status argument will be a pointer to a struct, containing the

179

node number, message type and error status of the received

180

message

181

182

say our last parameter is Status; then Status.MPI_SOURCE

183

184

will contain the number of the sending node, and

Status.MPI_TAG will contain the message type; these are

185

important if used MPI_ANY_SOURCE or MPI_ANY_TAG in our

186

node or tag fields but still have to know who sent the

187

message or what kind it is */

188

```

## 3 Message-Passing Mechanisms

#### 3.1 Message-Passing Hardware

#### 3.1.1 Hypercubes

A popular class of parallel machines used to be that of **hypercubes**. Intel sold them, for example. A hypercube would consist of some number of ordinary Intel processors, with each processor having some memory and serial I/O hardward for connection to its "neighbor" processors.

Hypercubes proved to be too expensive for the type of performance they could achieve, and the market was small anyway. Thus they are not common today, but they are still important, in that the algorithms developed for them have become quite popular for use on general machines. In this section we will discuss architecture, algorithms and software for such machines.

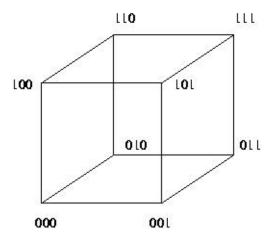

**Definitions** A hypercube of dimension d consists of  $D = 2^d$  processing elements (PEs), i.e. processor-memory pairs, We refer to such a cube as a **d-cube**.

The PEs in a d-cube will have numbers 0 through D-1. Let  $(c_{d-1},...,c_0)$  be the base-2 representation of a PE's number. The PE has fast point-to-point links to d other PEs, which we will call its **neighbors**. Its ith neighbor has number  $(c_{d-1},...,1-c_{i-1},...,c_0)$ .

<sup>&</sup>lt;sup>7</sup>Note that we number the digits from right to left, with the rightmost digit being digit 0.

For example, consider a hypercube having D=16, i.e. d=4. The PE numbered 1011, for instance, would have four neighbors, 0011, 1111, 1001 and 1010.

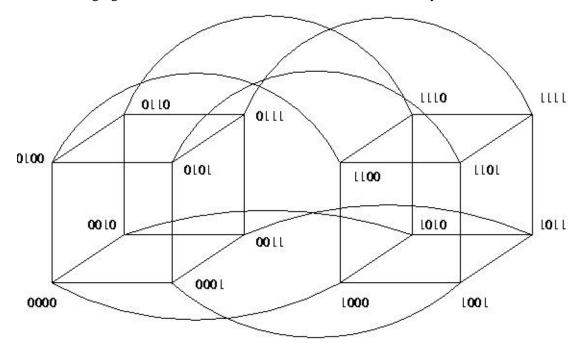

It is sometimes helpful to build up a cube from the lower-dimensional cases. To build a (d+1)-dimensional cube from two d-dimensional cubes, just follow this recipe:

- (a) Take a d-dimensional cube and duplicate it. Call these two cubes subcube 0 and subcube 1.

- (b) For each pair of same-numbered PEs in the two subcubes, add a binary digit 0 to the front of the number for the PE in subcube 0, and add a 1 in the case of subcube 1. Add a link between them.

The following figure shows how a 4-cube can be constructed in this way from two 3-cubes:

Introduction to Parallel Processing: 15

Given a PE of number  $(c_{d-1},...,c_0)$  in a d-cube, we will discuss the i-cube to which this PE belongs, meaning all PEs whose first d-i digits match this PE's.<sup>8</sup> Of all these PEs, the one whose last i digits are all 0s is called the **root** of this i-cube.

For the 4-cube and PE 1011 mentioned above, for instance, the 2-cube to which that PE belongs consists of 1000, 1001, 1010 and 1011—i.e. all PEs whose first two digits are 10—and the root is 1000.

Given a PE, we can split the i-cube to which it belongs into two (i-1)-subcubes, one consisting of those PEs whose digit i-1 is 0 (to be called subcube 0), and the other consisting of those PEs whose digit i-1 is 1 (to be called subcube 1). Each given PE in subcube 0 has as its **partner** the PE in subcube 1 whose digits match those of the given PE, except for digit i-1.

To illustrate this, again consider the 4-cube and the PE 1011. As an example, let us look at how the 3-cube it belongs to will split into two 2-cubes. The 3-cube to which 1011 belongs consists of 1000, 1001, 1010, 1011, 1100, 1101, 1110 and 1111. This 3-cube can be split into two 2-cubes, one being 1000, 1001, 1010 and 1011, and the other being 1100, 1101, 1110 and 1111. Then PE 1000 is partners with PE 1100, PE 1001 is partners with PE 1101, and so on.

Each link between two PEs is a dedicated connection, much preferable to the shared link we have when we run, say, MPI, on a collection of workstations on an Ethernet. On the other hand, if one PE needs to communicate with a <u>non</u>-neighbor PE, multiple links (as many as d of them) will need to be traversed. Thus the nature of the communications costs here is much different than for a network of workstations, and this must be borne in mind when developing programs.

#### 3.1.2 Networks of Workstations (NOWs)

As of this writing (early 2004), the commercial market for shared-memory hardware is strong, with the machines being used for heavy-duty server applications, such as for large databases and World Wide Web sites. The conventional wisdom is that these applications require the efficiency that good shared-memory hardware can provide. Nevertheless, the prices of these systems are enormous, and it is very unclear as to whether they can remain commercially viable.

Instead, the most promising alternative today appears to be networks of workstations (NOWs). It is much cheaper to purchase a set of workstations<sup>9</sup> and network them for use as parallel processing systems. They are of course individual machines, capable of the usual uniprocessor, nonparallel applications, but by networking them together and using parallel-processing software environments, we can form very powerful parallel systems.

The networking does result in a significant loss of performance. This will be discussed later. But even without these techniques, the price/performance ratio in NOW is much superior in many applications to that of specialized shared-memory or hypercube hardware.

One factor which can be key to the success of a NOW is to use a fast network, both in terms of hardware and network protocol. Ordinary Ethernet and TCP/IP are fine for the applications envisioned by the original

<sup>&</sup>lt;sup>8</sup>Note that this is indeed an i-dimensional cube, because the last i digits are free to vary.

<sup>&</sup>lt;sup>9</sup> I am including PCs in this category, as they are certainly as powerful today as the machines traditionally called "workstations."

designers of the Internet, e.g. e-mail and file transfer, but is slow in the NOW context. A good network for a NOW is, for instance, Infiniband. For information on network protocols, e.g. for example www.rdmaconsortium.org.

#### 3.1.3 Hardware Issues

Multiprocessor architects use the terms **latency** and **bandwidth** to provide a rough description of the performance potential of an interconnect. Latency means time it takes for a bit to travel from source to destination. This includes queuing delays within network nodes, software delays (as a bit travels through software layers, e.g. from application program to OS to I/O hardware), etc. Bandwidth means the number of bits which can be sent simultaneously.

In a message-passing system on an Ethernet, node-to-node communication latency is quite high, as high as hundreds of microseconds, which is huge compared to memory-latency time for (at least the smaller) shared-memory systems. This can be greatly reduced by using a special network, but in any case, when writing application software, failure to write the code in such a way as to deal with this latency issue can severely reduce program speed, sometimes even to the point at which running on a single machine is faster than running in parallel.

One remedy that one can try is to use **nonblocking** versions of Send() functions to reduce the effect of this latency. This means that a node does not have to wait for a message transmission to occur, but can instead work on other subtasks in the interim.

The newest message-passing hardware/software systems implement **active messages**. Here latency is actually reduced, because a message will be deposited directly into the application program's buffer at the receiver, rather than being buffered by the operating system first and then copied a second time to the application program's address space.

For example, consider the code

```

int X[1000000];

...

Recv(X);

```

The array X will be sent to this node by some other node, with a call something like

```

Send(X);

```

As this message arrives at the receiving node via the Ethernet, the Ethernet card at that node will cause a CPU interrupt. The interrupt service routine, i.e. the OS, will copy the incoming data from ports in the Ethernet card to a buffer in the OS. When done, that data will then be sent by the OS to the application program, which will, via Recv(), copy the data to X. In other words, we have only one copy operation to memory, not two, which can save a lot of time.

Another way to deal with latency is to hide it, rather than reduce it, using threading. If we are using message-passing, for instance, instead of waiting a long time to receive a message, we can switch to a different thread and do other useful work for our parallel processing task while we are waiting.

#### 3.1.4 Message Passing on Shared-Memory Machines

Even if one has shared-memory hardware, one can still do message-passing on it, say with MPI. In fact, IBM even produces its own version of MPI, especially tailored to IBM's shared-memory machines.

Why would one do this? Well, even though most people in the parallel processing community believe that the shared-memory programming paradigm is clearer than the message-passing paradigm, there is general agreement that if one wants to really get as much speed as possible on a given platform, message-passing is better able to attain top speed than shared-memory programming. Another reason for using message passing on a shared-memory machine, using MPI, is that the code is then usable on (if not optimized for) use on almost any platform.

#### 3.2 Message-Passing Software

The first widely-used message-passing software was PVM (Parallel Virtual Machine); see the links at http://heather.cs.ucdavis.edu/~matloff/pvm.html. It was developed at Oak Ridge National Laboratory. It is still in wide use today, but its successor MPI (Message Passing Interface); see the links at http://heather.cs.ucdavis.edu/~matloff/mpi.html. It was developed at Argonne National Laboratory is probably the more popular package now. Both PVM and MPI are public-domain.

## 4 Shared-Memory Mechanisms

#### 4.1 Hardware Issues

As mentioned in the message-passing setting above, when writing application software to run on such systems, failure to write the code in such a way as to deal with hardware issues can severely reduce program speed, sometimes even to the point at which running on a single machine is faster than running in parallel.

#### 4.2 Shared-Memory through Hardware

(Note: In spite of the word *hardware* in the title of this section, you will see later that many of the issues discussed here will also arise in software contexts.)

The term **shared memory** means that the processors all share a common address space. Say this is occurring at the hardware level, and we are using Intel Pentium CPUs. Suppose processor P3 issues the instruction

movl 200, %eabx

which reads memory location 200 and places the result in the EAX register in the CPU. If processor P4 does the same, they both will be referring to the same physical memory cell. In non-shared-memory machines, each processor has its own private memory, and each one will then have its own location 200, completely independent of the locations 200 at the other processors' memories.

Say a program contains a global variable X and a local variable Y on share-memory hardware (and we use shared-memory software). If for example the compiler assigns location 200 to the variable X, i.e. &X = 200, then the point is that all of the processors will have that variable in common, because any processor which issues a memory operation on location 200 will access the same physical memory cell.

On the other hand, each processor will have its own separate run-time stack, <sup>10</sup> and thus each processor will have its own independent copy of the local variable Y.

To make the meaning of "shared memory" more concrete, suppose we have a bus-based system, with all the processors and memory attached to the bus. Let us compare the above variables X and Y here. Suppose again that the compiler assigns X to memory location 200. Then in the machine language code for the program, every reference to X will be there as 200. Every time an instruction involving X is executed by a CPU, that CPU will put 200 into its Memory Address Register (MAR), from which the 200 flows out on the address lines in the bus, and goes to memory. This will happen in the same way no matter which CPU it is. Thus the same physical memory location will end up being accessed, no matter which CPU generated the reference.

By contrast, say the compiler assigns Y to something like ESP+8, the third item on the stack.<sup>11</sup> Each CPU will have its own current value for ESP, so the stacks of the various CPUs will be separate.<sup>12</sup>

#### 4.2.1 Placement of Memory Modules

The placement of the memory modules is quite important.

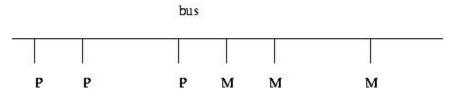

**Symmetric Multiprocessor** Let's first consider the following structure:

Here and below:

<sup>&</sup>lt;sup>10</sup>Still in shared memory, but a separate stack for each processor, since each CPU has a different value in its SP register.

<sup>&</sup>lt;sup>11</sup>ESP is the number of the stack pointer register in the Pentium.

<sup>&</sup>lt;sup>12</sup>Again, the stacks <u>will</u> be in the physical shared memory, and thus P3, say, could theoretically access P8's stack, say if there were an erroneous pointer value. But even that would not occur if we are using virtual memory and thus have protections against this.

- The Ps are processors, e.g. off-the-shelf chips such as Pentiums.

- The Ms are **memory modules**. These are physically separate objects, e.g. separate boards of memory chips. It is typical that there will be the same number of Ms as Ps, but it does not have to be this way. In the shared-memory case, the Ms collectively form the entire shared address space, but with the addresses being assigned to the Ms in one of two ways:

- (a)

High-order interleaving. Here consecutive addresses are in the <u>same</u> M (except at boundaries).

For example, suppose for simplicity that our memory consists of addresses 0 through 1023, and that there are four Ms. Then M0 would contain addresses 0-255, M1 would have 256-511, M2 would have 512-767, and M3 would have 768-1023.

- (b)

Low-order interleaving. Here consecutive addresses are in consecutive M's (except when we get to the right end). In the example above, if we used low-order interleaving, then address 0 would be in M0, 1 would be in M1, 2 would be in M2, 3 would be in M3, 4 would be back in M0, 5 in M1, and so on.

- To make sure only one P uses the bus at a time, standard bus arbitration signals and/or arbitration devices are used.

- There may also be **coherent caches**, which we will discuss later.

The shared-memory, bus-connected case shown here is called a **symmetric multiprocessor** (SMP). It is also referred to as a Uniform Memory Access (UMA) structure, meaning that all CPUs have the same access time to memory. Except for the negligible difference in bus propagation delays, each processor takes the same time to acquire the bus and then access memory.

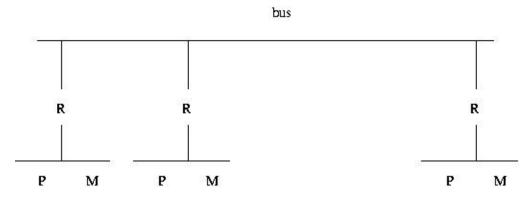

#### **A NUMA Example** By contrast, look at this version:

Each P/M/R set here is called a **processing element** (PE). Note that each PE has its own local bus, and is also connected to the global bus via R, the router.

<sup>&</sup>lt;sup>13</sup>Miscellaneous gates ("glue") would be used so that the correct M would recognize a bus address as being for that M.

Suppose for example that P3 needs to access location 200, and suppose that high-order interleaving is used.<sup>14</sup> If location 200 is in M3, then P3's request is satisfied by the local bus.<sup>15</sup> On the other hand, suppose location 200 is in M8. Then the R3 will notice this, and put the request on the global bus, where it will be seen by R8, which will then copy the request to the local bus at PE8, where the request will be satisfied. (E.g. if it was a read request, then the response will go back from M8 to R8 to the global bus to R3 to P3.)

It should be obvious now where NUMA gets its name. P8 will have much faster access to M8 than P3 will to M8, if none of the buses is currently in use—and if say the global bus is currently in use, P3 will have to wait a long time to get what it wants from M8.

These days NUMA systems are really in vogue. One of the attractive features of NUMA is that by good programming we can exploit the nonuniformity. In matrix problems, for example, we can write our program so that, for example, P8 usually works on those rows of the matrix which are stored in M8, P3 usually works on those rows of the matrix which are stored in M3, etc. In order to do this, we need to make use of the C language's & address operator, and have some knowledge of the memory hardware structure, i.e. the interleaving.

#### 4.2.2 Interconnect Topologies

The problem with a bus connection, of course, is that there is only one pathway for communication, and thus only one processor can access memory at the same time. If one has more than, say, two dozen processors are on the bus, the bus becomes saturated, even if traffic-reducing methods such as adding caches are used. Thus multipathway topologies are used for all but the smallest systems. In this section we look at two alternatives to a bus topology.

**Crossbar Interconnects** Consider a UMA shared-memory system with n processors and n memory modules. The a crossbar connection would provide  $n^2$  pathways. E.g. for n = 8:

<sup>&</sup>lt;sup>14</sup> Low-order interleaving would probably be disastrous here.

<sup>&</sup>lt;sup>15</sup>This sounds similar to the concept of a cache. However, it is very different. A cache contains a local copy of some data stored elsewhere. Here it is the data itself, not a copy, which is being stored locally.

Generally serial communication is used from node to node, with a packet containing information on both source and destination address. E.g. if P2 wants to read from M5, the source and destination will be 3-bit strings in the packet, coded as 010 and 101, respectively. The packet will also contain bits which specify which word within the module we wish to access, and bits which specify whether we wish to do a read or a write. In the latter case, additional bits are used to specify the value to be written.

Each diamond-shaped node has two inputs (bottom and right) and two outputs (left and top), with buffers at the two inputs. If a buffer fills, there are two design options: (a) Have the node from which the input comes block at that output. (b) Have the node from which the input comes discard the packet, and retry later, possibly outputting some other packet for now. If the packets at the heads of the two buffers both need to go out the same output, the one (say) from the bottom input will be given priority.

In this UMA setting, 16 there would also be a return network of the same type, with this one being memory

Note that we are calling it UMA because processors and memory modules are not paired together. The access is not really very uniform.

→ processor, to return the result of the read requests. 17

A NUMA version of this is also possible. It is not shown here, but the difference would be that at the bottom edge we would have the PEi and at the left edge the memory modules Mi would be replaced by lines which wrap back around to PEi. 18

Crossbar switches are too expensive for large-scale systems, but are useful in some small systems. The 16-CPU Sun Microsystems Enterprise 10000 system includes a 16x16 crossbar.

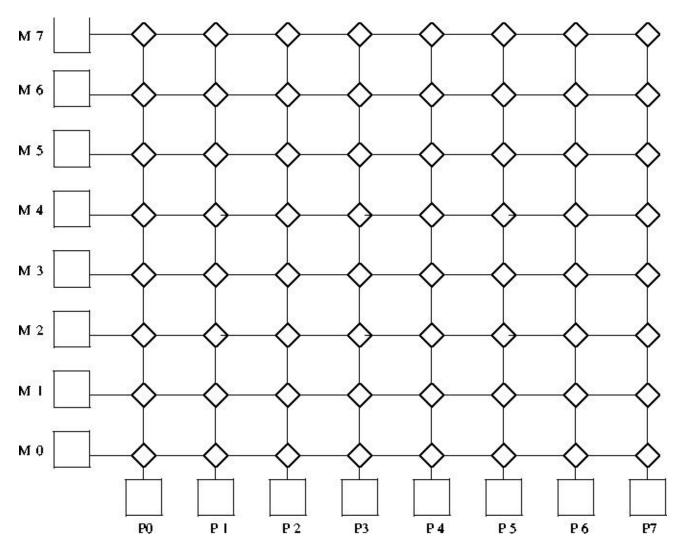

**Omega Interconnects** These are multistage networks similar to crossbars, but with fewer paths. Here is an example of a NUMA 8x8 system:

Recall that each PE is a processor/memory pair. PE3, for instance, consists of P3 and M3.

Note the fact that at the third stage of the network (top of picture), the outputs are routed back to the PEs, each of which consists of a processor and a memory module.<sup>19</sup>

In a UMA version, we would see Pi instead of PEi at the bottom edge, and would see Mi at the top edge instead of dashed lines leading downward.

At each network node (the nodes are the three rows of rectangles), the output routing is done by destination bit. Let's number the stages here 0, 1 and 2, starting from the bottom stage, number the nodes within a stage 0, 1, 2 and 3 from left to right, number the PEs from 0 to 7, left to right, and number the bit positions in a destination address 0, 1 and 2, starting from the most significant bit. Then at stage i, bit i of the destination address is used to determine routing, with a 0 meaning routing out the left output, and 1 meaning the right one.

Say P2 wishes to read from M5. It sends a read-request packet, including 5 = 101 as its destination address, to the switch in stage 0, node 1. Since the first bit of 101 is 1, that means that this switch will route the packet out its right-hand output, sending it to the switch in stage 1, node 3. The latter switch will look at the next bit in 101, a 0, and thus route the packet out its left output, to the switch in stage 2, node 2. Finally, that switch will look at the last bit, a 1, and output out its right-hand output, sending it to PE5, as desired. M5 will process the read request, and send a packet back to PE2, along the same

Again, if two packets at a node want to go out the same output, one must get priority (let's say it is the one from the left input).

<sup>&</sup>lt;sup>17</sup> For safety's sake, i.e. fault tolerance, even writes are typically acknowledged in multiprocessor systems.

<sup>&</sup>lt;sup>18</sup>Similar to the Omega network shown below.

<sup>&</sup>lt;sup>19</sup>The picture may be cut off somewhat at the top and left edges. The upper-right output of the rectangle in the top row, leftmost position should connect to the dashed line which leads down to the second PE from the left. Similarly, the upper-left output of that same rectangle is a dashed lined, possibly invisible in your picture, leading down to the leftmost PE.

Here is how the more general case of  $N=2^n$  PEs works. Again number the rows of switches, and switches within a row, as above. So,  $S_{ij}$  will denote the switch in the i-th row from the bottom and j-th column from the left (starting our numbering with 0 in both cases). Row i will have a total of N input ports  $I_{ik}$  and N output ports  $O_{ik}$ , where k=0 corresponds to the leftmost of the N in each case. Then if row i is not the last row (i < n-1),  $O_{ik}$  will be connected to  $I_{jm}$ , where j=i+1 and

$$m = (2k + \lfloor (2k)/N \rfloor) \bmod N \tag{1}$$

If row i is the last row, then  $O_{ik}$  will be connected to, PE k.

**Comparative Analysis** In the world of parallel architectures, a key criterion for a proposed feature is **scalability**, meaning how well the feature performs as we go to larger and larger systems. Let n be the system size, either the number of processors and memory modules, or the number of PEs. Then we are interested in how fast the latency, bandwidth and cost grow with n:

| criterion | bus  | Omega           | crossbar |

|-----------|------|-----------------|----------|

| latency   | O(1) | $O(\log_2 n)$   | O(n)     |

| bandwidth | O(1) | O(n)            | O(n)     |

| cost      | O(1) | $O(n \log_2 n)$ | $O(n^2)$ |

Let us see where these expressions come from, beginning with a bus: No matter how large n is, the time to get from, say, a processor to a memory module will be the same, thus O(1). Similarly, no matter how large n is, only one communication can occur at a time, thus again O(1).

Again, we are interested only in "O()" measures, because we are only interested in growth rates as the system size n grows. For instance, if the system size doubles, the cost of a crossbar will quadruple; the  $O(n^2)$  cost measure tells us this, with any multiplicative constant being irrelevant.

For Omega networks, it is clear that  $log_2n$  network rows are needed, hence the latency value given. Also, each row will have n/2 switches, so the number of network nodes will be  $O(n log_2n)$ . This figure then gives the cost (in terms of switches, the main expense here). It also gives the bandwidth, since the maximum number of simultaneous transmissions will occur when all switches are sending at once.

Similar considerations hold for the crossbar case.

The crossbar's big advantage is that it is guaranteed that n packets can be sent simultaneously, providing they are to distinct destinations.<sup>21</sup>

That is <u>not</u> true for Omega-networks. If for example, PE0 wants to send to PE3, and at the same time PE4 wishes to sent to PE2, the two packets will clash at the leftmost node of stage 1, where the packet from PE0 will get priority.

<sup>&</sup>lt;sup>20</sup> Note that the '1' in "O(1)" does not refer to the fact that only one communication can occur at a time. If we had, for example, a two-bus system, the bandwidth would still be O(1), since multiplicative constants do not matter. What O(1) means, again, is that as n grows, the bandwidth stays at a multiple of 1, i.e. stays constant.

<sup>&</sup>lt;sup>21</sup> If two or more go to the same destination, they couldn't be satisfied simultaneously anyway, unless dual-port memory were used.

On the other hand, a crossbar is very expensive, and thus is dismissed out of hand in most modern systems. Note, though, that an equally troublesom aspect of crossbars is their high latency value; this is a big drawback when the system is not heavily loaded.

The bottom line is that Omega-networks amount to a compromise between buses and crossbars, and for this reason have become popular.

#### 4.2.3 Test-and-Set

Consider a bus-based UMA system. In addition to whatever memory read and memory write instructions the processor included, say LD and ST, there would also be a TAS instruction.<sup>22</sup> This instruction would control a TAS pin on the processor chip, and the pin in turn would be connected to a TAS line on the bus.

Applied to a location L in memory and a register R, say, TAS does the following:

```

copy L to R if R is 0 then write 1 to L

```

And most importantly, these operations are done in an **atomic** manner; no bus transactions by other processors may occur between the two steps.

The TAS operation is applied to variables used as **locks**. Let's say that 1 means locked and 0 unlocked. Then the guarding of a critical section C by a lock variable L would be done by having the following code in the program being run:

where of course JNZ is a jump-if-nonzero instruction, and we are assuming that the copying from the Memory Data Register to R results in the processor N and Z flags (condition codes) being affected.

A **critical section** is a portion of a program in which we cannot have more than one processor execute at a time. For instance, consider an airline reservation system. If a flight has only one seat left, we want to avoid giving it to two different customers who might be talking to two agents at the same time. The lines of code in which the seat is finally assigned (the **commit** phase, in database terminology) is then a critical section.

In crossbar or  $\Omega$ -network systems, some 2-bit field in the packet must be devoted to transaction type, say 00 for Read, 01 for Write and 10 for TAS. In a sytem with 16 CPUs and 16 memory modules, say, the packet might consist of 4 bits for the CPU number, 4 bits for the memory module number, 2 bits for the transaction type, and 32 bits for the data (for a write, this is the data to be written, while for a read, it would be the requested value, on the trip back from the memory to the CPU).

<sup>&</sup>lt;sup>22</sup>This discussion is for a mythical machine, but any real system works in this manner.

But note that the atomicity here is best done at the memory, i.e. some hardware should be added at the memory so that TAS can be done; otherwise, an entire processor-to-memory path (say in a UMA system) would have to be locked up for a fairly long time, obstructing even the packets which go to other memory modules.

There are many variations of test-and-set, so don't expect that all processors will have an instruction with this name, but they all will have some kind of synchronization instruction like it.

Note carefully that in many settings it may not be crucial to get the most up-to-date value of a variable. For example, a program may have a data structure showing work to be done. Some processors occasionally add work to the queue, and others take work from the queue. Suppose the queue is currently empty, and a processor adds a task to the queue, just as another processor is checking the queue for work. As will be seen later, it is possible that even though the first processor has written to the queue, the new value won't be visible to other processors for some time. But the point is that if the second processor does not see work in the queue (even though the first processor has put it there), the program will still work correctly, albeit with some performance loss.

#### 4.2.4 Cache Coherency

Consider, for example, a bus-based system. Relying purely on TAS for interprocessor synchronization would be unthinkable: As each processor contending for a lock variable spins in the loop shown above, it is adding tremendously to bus traffic.

An answer is to have caches at each processor.<sup>23</sup> These will to store copies of the values of lock variables. (Of course, non-lock variables are stored too. However, the discussion here will focus on effects on lock variables.) The point is this: Why keep looking at a lock variable L again and again, using up the bus bandwidth? L may not change value for a while, so why not keep a copy in the cache, avoiding use of the bus?

The answer of course is that eventually L will change value, and this causes some delicate problems. Say for example that processor P5 wishes to enter a critical section guarded by L, and that processor P2 is already in there. During the time P2 is in the critical section, P5 will spin around, always getting the same value for L (1) from C5, P5's cache. When P2 leaves the critical section, P2 will set L to 0—and now C5's copy of L will be incorrect. This is the **cache coherency problem**, inconsistency between caches.

A number of solutions have been devised for this problem. For bus-based systems, **snoopy** protocols of various kinds are used, with the word "snoopy" referring to the fact that all the caches monitor ("snoop on") the bus, watching for transactions made by other caches.

The most common protocols are the **invalidate** and **update** types. This relation between these two is somewhat analogous to the relation between **write-back** and **write-through** protocols for caches in uniprocessor systems:

• Under an invalidate protocol, when a processor writes to a variable in a cache, it first (i.e. before

<sup>&</sup>lt;sup>23</sup>The reader may wish to review the basics of caches. See for example http://heather.cs.ucdavis.edu/ mat-loff/50/PLN/CompOrganization.pdf.

actually doing the write) tells each other cache to mark as invalid its cache line (if any) which contains a copy of the variable.<sup>24</sup> Those caches will be updated only later, the next time their processors need to access this cache line.

• For an update protocol, the processor which writes to the variable tells all other caches to immediately update their cache lines containing copies of that variable with the new value.

Let's look at an outline of how one implementation (many variations exist) of an invalidate protocol would operate:

In the scenario outlined above, when P2 leaves the critical section, it will write the new value 0 to L. Under the invalidate protocol, P2 will post an invalidation message on the bus. All the other caches will notice, as they have been monitoring the bus. They then mark their cached copies of the line containing L as invalid.

Now, the next time P5 executes the TAS instruction—which will be very soon, since it is in the loop shown above—P5 will find that the copy of L in C5 is invalid. It will respond to this cache miss by going to the bus, and requesting P2 to supply the "real" (and valid) copy of the line containing L.

But there's more. Suppose that all this time P6 had also been executing the loop shown above. Then P5 and P6 may have to contend with each other; whoever manages to grab possession of the bus first<sup>25</sup> will be the one who ends up finding that L=0. Let's say that that one is P6. P6 then executes the TAS again, finds L=0, and then enters the critical section. An instant later, P5 P6 relinquishes the bus, P5 tries its execution of the TAS again. P5 acquires a valid copy of L now, but L will be 1 at this time, so P5 must resume executing the loop. P5 will then continue to use its valid local copy of L each time it does the TAS, until P6 leaves the critical section, writes 0 to L, and causes another cache miss at P5, etc.

At first the update approach seems obviously superior, and actually, if our shared, cacheable<sup>26</sup> variables were only lock variables, this might be true.

But consider a shared, cacheable vector. Suppose the vector fits into one block, and that we write to each vector element sequentially. Under an update policy, we would have to send a new message on the bus/network for each component, while under an invalidate policy, only one message (for the first component) would be needed. If during this time the other processors do not need to access this vector, all those update messages, and the bandwidth they use, would be wasted.

Or suppose for example we have code like

```

Sum += X[I];

```

in the middle of a **for** loop. Under an update protocol, we would have to write the value of Sum back many times, even though the other processors may only be interested in the final value when the loop ends. (This would be true, for instance, if the code above were part of a critical section.)

<sup>&</sup>lt;sup>24</sup>we will follow commonly-used terminology here, distinguishing between a *cache line* and a *memory block*. Memory is divided in blocks, some of which have copies in the cache. The cells in the cache are called *cache lines*. So, at any given time, a given cache line is either empty or contains a copy (valid or not) of some memory block.

<sup>&</sup>lt;sup>25</sup>Again, remember that ordinary bus arbitration methods would be used.

<sup>&</sup>lt;sup>26</sup> Many modern processors, including Pentium and MIPS, allow the programmer to mark some blocks as being noncacheable.

If you have previously studied **write-back** and **write-through** cache policies on uniprocessor systems, you should note the similarities of the issues here. Note, though, that the problems are exacerbated here, due to the high cost of communication, e.g. bus contention.

Thus the invalidate protocol works well for some kinds of code, while update works better for others. The CPU designers must try to anticipate which protocol will work well across a broad mix of applications.<sup>27</sup>

Now, how is cache coherency handled in non-bus shared-memory systems, say crossbars? Here the problem is more complex. Think back to the bus case for a minute: The very feature which was the biggest negative feature of bus systems—the fact that there was only one path between components made bandwidth very limited—is a very <u>positive</u> feature in terms of cache coherency, because it makes <u>broadcast</u> very easy: Since everyone is attached to that single pathway, sending a message to all of them costs no more than sending it to just one—we get the others for free. That's no longer the case for multipath systems. In such systems, extra copies of the message must be created for each path, adding to overall traffic.

A solution is to send messages only to "interested parties." In **directory-based** protocols, a list is kept of all caches which currently have valid copies of all blocks. In one common implementation, for example, while P2 is in the critical section above, it would be the **owner** of the block containing L. (Whoever is the latest node to write to L would be considered its current owner.) It would maintain a directory of all caches having valid copies of that block, say C5 and C6 in our story here. As soon as P2 wrote to L, it would then send either invalidate or update packets (depending on which type was being used) to C5 and C6 (and <u>not</u> to other caches which didn't have valid copies).

There would also be a directory at the memory, listing the current owners of all blocks. Say for example P0 now wishes to "join the club," i.e. tries to access L, but does not have a copy of that block in its cache C0. C0 will thus not be listed in the directory for this block. So, now when it tries to access L and it will get a cache miss. P0 must now consult the **home** of L, say P14. The home might be determined by L's location in main memory according to high-order interleaving; it is the place where the main-memory version of L resides. A table at P14 will inform P0 that P2 is the current owner of that block. P0 will then send a message to P2 to add C0 to the list of caches having valid copies of that block. Similarly, a cache might "resign" from the club, due to that cache line being replaced, e.g. in a LRU setting, when some other cache miss occurs.

**Example: the MESI Cache Coherency Protocol** Many types of cache coherency protocols have been proposed and used, some of them quite complex. A relatively simple one for snoopy bus systems which is widely used is MESI, whose name stands for the four states a given cache line can be in for a given CPU:

- Modified

- Exclusive

- Shared

- Invalid

It is the protocol used in the Pentium I, for example.

<sup>&</sup>lt;sup>27</sup>Some protocols change between the two modes dynamically.

|  | summary |  |  |

|--|---------|--|--|

|  |         |  |  |

|  |         |  |  |

| state | meaning                                             |  |  |  |  |  |

|-------|-----------------------------------------------------|--|--|--|--|--|

| M     | M written to more than once; no other copy valid    |  |  |  |  |  |

| Е     | valid; no other cache copy valid; memory copy valid |  |  |  |  |  |

| S     | valid; at least one other cache copy valid          |  |  |  |  |  |

| I     | invalid                                             |  |  |  |  |  |

Following is a summary of MESI state changes.<sup>28</sup> When reading it, keep in mind that there is a separate state for each cache/memory block combination. In other words, if we have c CPUs (and thus c caches) and b memory blocks, there are components in a state. Also, in addition to the terms **read hit**, **read miss**, **write hit**, **write miss**, which you are already familiar with, there are also **read snoop** and **write snoop**. These refer to the case in which our CPU observes a read or write action by another CPU on the bus. So, here are various events and their corresponding state changes:

#### If our CPU does a read:

| present state | event                                                      | new state |

|---------------|------------------------------------------------------------|-----------|

| M             | read hit                                                   | M         |

| Е             | read hit                                                   | Е         |

| S             | read hit                                                   | S         |

| I             | read miss; no valid cache copy at any other CPU            | Е         |

| I             | read miss; at least one valid cache copy in some other CPU | S         |

## If our CPU does a memory write:

| present state | event                                                                | new state |

|---------------|----------------------------------------------------------------------|-----------|

| M             | write hit; do not put invalidate signal on bus; do not update memory | M         |

| Е             | E same as M above                                                    |           |

| S             | write hit; put invalidate signal on bus; update memory               | Е         |

| I             | write miss; update memory but do nothing else                        | I         |

**If our CPU does a read snoop** (i.e. observes another CPU's cache do a read action on the bus) or **write snoop** (i.e. observes another CPU's cache to a write action on the bus):

| present state | event                                                           | newstate |  |  |

|---------------|-----------------------------------------------------------------|----------|--|--|

| M             | M read snoop; write line back to memory, picked up by other CPU |          |  |  |

| M             | write snoop; write line back to memory                          | I        |  |  |

| Е             | read snoop; put shared signal on bus; no memory action          | S        |  |  |

| Е             | write snoop; no memory action                                   | I        |  |  |

| S             | read snoop                                                      | S        |  |  |

| S             | write snoop                                                     | I        |  |  |

| I             | any snoop                                                       | I        |  |  |

<sup>&</sup>lt;sup>28</sup>See *Pentium Processor System Architecture*, by D. Anderson and T. Shanley, Addison-Wesley, 1995. We have simplified the presentation here, by eliminating certain programmable options.

#### 4.2.5 The Problem of "False Sharing"

Consider the C declaration

int W,Z;

Since W and Z are declared adjacently, most compilers will assign them contiguous memory addresses. Thus, unless one of them is at a memory block boundary, when they are cached they will be stored in the same cache line. Suppose the program writes to Z, and our system uses an invalidate protocol. Then W will be considered invalid at the other processors, even though its values at those processors' caches are correct. This is the **false sharing** problem, alluding to the fact that the two variables are sharing a cache line even though they are not related.

This can have very adverse impacts on performance. If for instance our variable **W** is now written to, then **Z** will suffer unfairly, as its copy in the cache will be considered invalid even though it is perfectly valid. This can lead to a "ping-pong" effect, in which alternate writing to two variables leads to a cyclic pattern of coherency transactions.

#### 4.2.6 Memory-Access Consistency Policies

Though the word *consistency* in the title of this section may seem to simply be a synonym for *coherency* from the last section, and though there actually is some relation, the issues here are quite different. In this case, it is a timing issue: After one processor changes the value of a shared variable, when will that value be visible to the other processors?

There are various reasons why this is an issue. For example, many processors, especially in multiprocessor systems, have **write buffers**, which save up writes for some time before actually sending them to memory. (For the time being, let's suppose there are no caches.) The goal is to reduce memory access costs. Sending data to memory in groups is generally faster than sending one at a time, as the overhead of, for instance, acquiring the bus is amortized over many accesses. Reads following a write may proceed, without waiting for the write to get to memory, except for reads to the same address. So in a multiprocessor system in which the processors use write buffers, there will often be some delay before a write actually shows up in memory.

A related issue is that operations may occur, or appear to occur, out of order. As noted above, a read which follows a write in the program may execute before the write is sent to memory. Also, in a multiprocessor system with multiple paths between processors and memory modules, two writes might take different paths, one longer than the other, and arrive "out of order." In order to simplify the presentation here, we will focus on the case in which the problem is due to write buffers, though.

The designer of a multiprocessor system must adopt some **consistency model** regarding situations like this. The above discussion shows that the programmer must be made aware of the model, or risk getting incorrect results. Note also that different consistency models will give different levels of performance. The "weaker" consistency models make for faster machines but require the programmer to do more work.

The strongest consistency model is Sequential Consistency. It essentially requires that memory operations done by one processor are observed by the other processors to occur in the same order as executed on the

first processor. Enforcement of this requirement makes a system slow, and it has been replaced on most systems by weaker models.